# August 2007

# FDMS2380 Dual Integrated Solenoid Driver

FAIRCHILD SEMICONDUCTOR®

# FDMS2380

**Dual Integrated Solenoid Driver**

# Features

- 5A, 60V Load Clamp

- $r_{DS(ON)} = 30m\Omega$  (Typ.) Excitation path

- 6V to 26V Operation

- CMOS Compatible

- Soft Short Detection

- Thermal Shutdown

- Diagnostic Output

- Integrated Clamps

- Over-current Protection

- Open Load Detection

- Over-voltage Protection

# Applications

- Transmission Solenoid Driver

- Inductive Load Management

# **General Description**

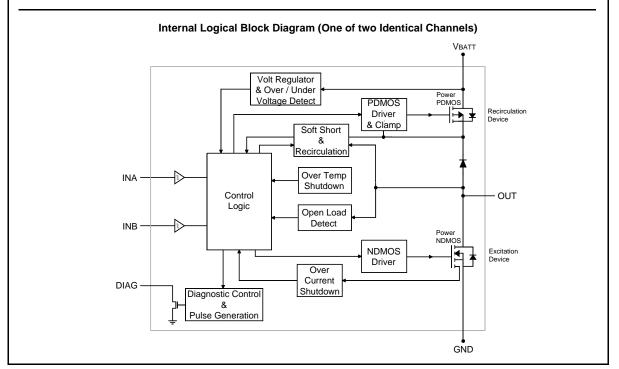

The FDMS2380 is an intelligent low side driver with built in recirculation and demagnetization circuits designed specifically for driving inductive loads. The inputs are CMOS compatible. A separate diagnostic signal for each channel provides the system with an indication of the operation of the solenoid or the presence of a protection fault condition. Built-in Over-voltage, Over-current, Over-temperature circuits protect the device from these conditions. Additional diagnostic circuitry is included for detecting Open Load, Under-voltage and output ground fault conditions. The FDMS2380 contains two independent intelligent low side solenoid drivers.

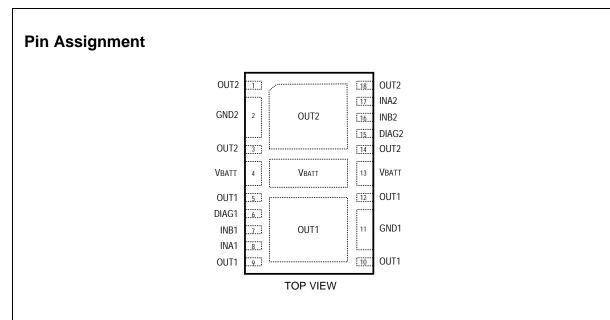

# **Pin Description**

| •                            |                   |                                                                   |  |

|------------------------------|-------------------|-------------------------------------------------------------------|--|

| QFN Pin                      | Pin Name          | Pin Description                                                   |  |

| 1, 3, 14, 18, pad OUT2       | OUT2              | Power Driver Output (Ch2)                                         |  |

| 2                            | GND2              | Ground (Ch2)                                                      |  |

| 4, 13, pad V <sub>BATT</sub> | V <sub>BATT</sub> | Battery Supply Voltage. Battery supply is common to both channels |  |

| 5, 9, 10, 12, pad OUT1       | OUT1              | Power Driver Output (Ch1)                                         |  |

| 6                            | DIAG1             | Diagnostic Flag (Ch1). Open drain output.                         |  |

| 7                            | INB1              | Input Control Signal B (Ch1)                                      |  |

| 8                            | INA1              | Input Control Signal A (Ch1)                                      |  |

| 11                           | GND1              | Ground (Ch1)                                                      |  |

| 15                           | DIAG2             | Diagnostic Flag (Ch2). Open drain output.                         |  |

| 16                           | INB2              | Input Control Signal B (Ch2)                                      |  |

| 17                           | INA2              | Input Control Signal A (Ch2)                                      |  |

| Symbol                            | Parameter                                                            | Ratings    | Units |

|-----------------------------------|----------------------------------------------------------------------|------------|-------|

| I <sub>OUT(rev)</sub>             | Maximum Reverse Output Current                                       | -4         | А     |

| V <sub>BATT(max)</sub>            | Maximum DC Supply Voltage (Note 2)                                   | 60         | V     |

| I <sub>IN</sub>                   | Input Currents                                                       | 10         | mA    |

| V <sub>IN(max)</sub>              | Maximum Input Voltage                                                | 8          | V     |

| I <sub>DIAG</sub>                 | Diagnostic Output Current                                            | 10         | mA    |

| V <sub>DIAG(max)</sub>            | Maximum Diagnostic Output Voltage                                    | 8          | V     |

|                                   | Total Power dissipation                                              | 7          | W     |

| PD                                | Power dissipation V <sub>BATT</sub> pad                              | 2.3        | W     |

|                                   | Power dissipation OUT pads: $P_{D(OUT)} = P_{D(OUT1)} + P_{D(OUT2)}$ | 4.6        | W     |

| T <sub>J</sub> , T <sub>STG</sub> | Operating and Storage Temperature                                    | -40 to 160 | °C    |

### **Thermal Characteristics**

| $R_{\thetaJC}$  | Thermal Resistance Junction to Case: OUT pad                           | 3.5 | °C/W |

|-----------------|------------------------------------------------------------------------|-----|------|

| $R_{\theta JC}$ | Thermal Resistance Junction to Case: VBATT pad                         | 4.0 | °C/W |

| $R_{\thetaJA}$  | Thermal Resistance Junction to Ambient: OUT pad (Note 1)               | 60  | °C/W |

| $R_{\thetaJA}$  | Thermal Resistance Junction to Ambient: V <sub>BATT</sub> pad (Note 1) | 60  | °C/W |

# **Ordering Information**

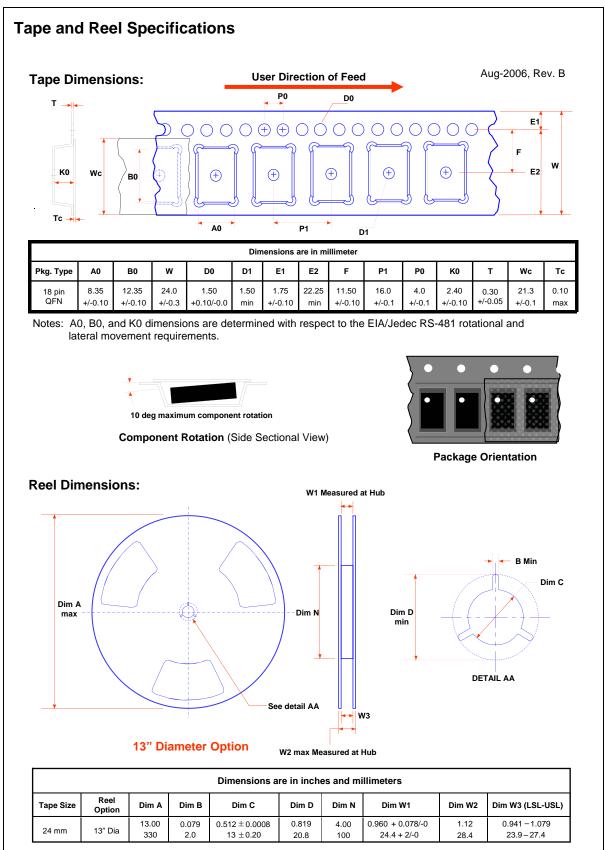

| Part Number | Package    | Packing<br>Method | Reel Size | Tape Width | Quantity |

|-------------|------------|-------------------|-----------|------------|----------|

| FDMS2380    | 18 pin QFN | Tape & Reel       | 330mm     | 24mm       | 2000     |

Notes:

1.  $R_{\theta JA}$  is measured with 1.0 in<sup>2</sup> copper on FR-4 board.  $R_{\theta JC}$  is guaranteed by design while  $R_{\theta JA}$  is determined by the user's board design.

2. The FDMS2380 requires one or more high quality local bypass capacitors (i.e., low ESL, low ESL and located physically close to the VBATT/Ground terminals of the device) to prevent fast transients on the V<sub>BATT</sub> line from affecting the operation of the device. More specifically, the bypass scheme must reduce transients with an amplitude passing through V<sub>BATT(ov)</sub> to have a rise time of less than 2.2V/µs.

| Symbol                   | Parameter                                                                       | Test Conditions                                                  | Min | Тур   | Max   | Units |

|--------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------|-----|-------|-------|-------|

| Off Chara                | acteristics                                                                     |                                                                  |     |       |       |       |

| V <sub>BATT(Oper)</sub>  |                                                                                 |                                                                  | 6.0 | 14.0  | 26.0  | V     |

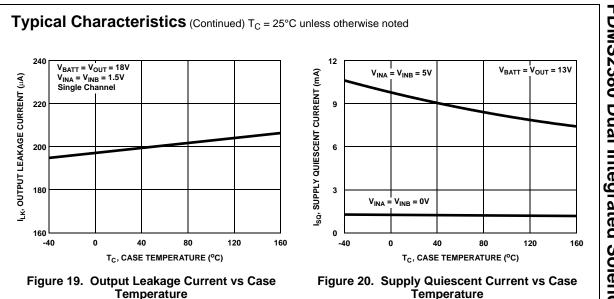

| I <sub>SQ</sub>          | Supply Quiescent Current                                                        | $V_{BATT} = 13V, V_{INA} = V_{INB} = 5V$                         | -   | 9.3   | 15    | mA    |

| I <sub>LK</sub>          | Output Leakage Current                                                          | $V_{BATT} = 18V$ , $V_{INA} = V_{INB} = 1.5V$                    | -   | 0.2   | 5     | mA    |

|                          | acteristics                                                                     | 1                                                                |     |       |       |       |

|                          |                                                                                 | $V_{BATT} = 13V, V_{INA} = V_{INB} = 5V,$                        | -   | 0.030 | 0.080 | Ω     |

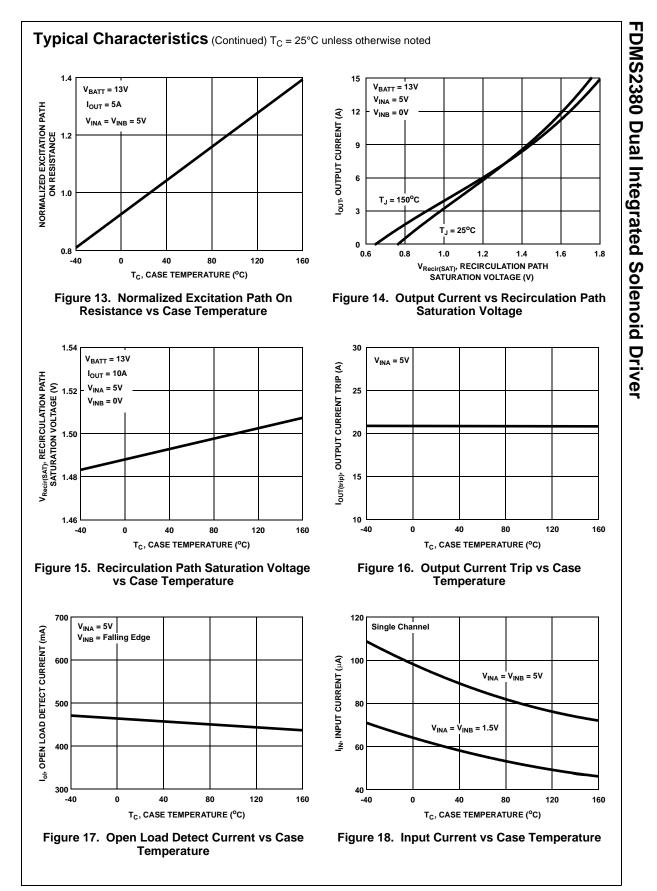

| r <sub>DS(ON)</sub>      | On Resistance - Excitation Path                                                 | $I_{OUT} = 5A$ $T_C = 150^{\circ}C$                              | -   | 0.050 | 0.100 | Ω     |

| V <sub>Recir(sat)</sub>  | Saturation Voltage - Recirculation<br>Path                                      | $V_{BATT} = 13V, V_{INA} = 5V,$<br>$V_{INB} = 0V, I_{OUT} = 10A$ | -   | 1.4   | 1.8   | V     |

| Switchin                 | g Characteristics (Excitation Pat                                               | :h)                                                              |     | •     |       |       |

| t <sub>d(ON)</sub>       | Output Turn-On Delay Time                                                       | <i>,</i>                                                         | -   | 7.0   | 30    | μS    |

|                          | Output Turn-Off Delay Time                                                      |                                                                  | -   | 8.3   | 30    | μS    |

| t <sub>r</sub>           | Rise Time                                                                       | $V_{BATT} = 14V, R_{Load} = 2.5\Omega$                           | -   | 6.5   | 10    | μS    |

| t <sub>f</sub>           | Fall Time                                                                       | 1                                                                | -   | 3.0   | 10    | μS    |

|                          | but Characteristics                                                             | 1                                                                |     |       |       |       |

|                          | Input Low Level Voltage                                                         |                                                                  | -   | -     | 1.5   | V     |

| V <sub>IH</sub>          | Input High Level Voltage                                                        |                                                                  | 3.5 | -     | -     | V     |

| V <sub>CL</sub>          | Input Clamp Voltage                                                             | I <sub>IN</sub> <=10mA                                           | 5.5 | -     | -     | V     |

|                          |                                                                                 | $V_{\rm INA} = V_{\rm INB} = 5V$                                 | -   | 90    | 160   | μA    |

| I <sub>IN</sub>          | Input Current (each input)                                                      | $V_{INA} = V_{INB} = 1.5V$                                       | 20  | 60    | -     | μA    |

| Protectio                | n and Diagnostics Character                                                     | istics (Note 1)                                                  |     | 1     |       |       |

|                          | Thermal Shut-down Junction                                                      |                                                                  | 100 | 470   | 405   | °C    |

| T <sub>J(tsd)</sub>      | Temperature                                                                     |                                                                  | 160 | 172   | 185   | °C    |

| I <sub>OUT(trip)</sub>   | Output Current Trip                                                             |                                                                  | 15  | 20    | 30    | А     |

| V <sub>BATT(ov)</sub>    | Over-voltage Threshold                                                          |                                                                  | 27  | 29    | 32    | V     |

| V <sub>BATT(uv)</sub>    | Under-voltage Threshold                                                         |                                                                  | -   | 5.1   | 5.5   | V     |

| I <sub>OUT(ol)</sub>     | Open Load Detect Current                                                        | $V_{INA} = 5V, V_{INB} = $ falling edge                          | 300 | 450   | 800   | mA    |

| V <sub>OUT(SS)</sub>     | Soft Short Detect Voltage                                                       | INA=0, INB=1, V <sub>BATT</sub> – V <sub>OUT</sub>               | 0.3 | 0.43  | 0.6   | V     |

| R <sub>SS</sub>          | Soft Short Resistance                                                           | INA=0, INB=1, from $V_{OUT}$ to $V_{BATT}$                       | 50  | 75    | 140   | Ω     |

| T <sub>SS</sub>          | Soft Short Active Time                                                          | INA=0, INB=1, time R <sub>SS</sub> is active                     | 1   | -     | 3     | ms    |

| V <sub>OUT(cl1)</sub>    | NDMOS Over-voltage Clamp                                                        | Ref to GND; I <sub>OUT</sub> = 5A                                | 60  | 73    | 85    | V     |

| V <sub>OUT(cl2)</sub>    | Output Inductive Clamp Voltage                                                  | V <sub>OUT</sub> – V <sub>BATT</sub> ; I <sub>OUT</sub> = 5A     | 27  | 30    | 33    | V     |

| V <sub>FB</sub>          | Flyback Diagnostic Threshold<br>Voltage (V <sub>OUT</sub> – V <sub>BATT</sub> ) | Threshold where DIAG goes low during Fast turn-off Mode          | 22  | 23    | 33    | V     |

| td <sub>(DIAG)</sub>     | Diagnostic Propagation Delay Time                                               | Fast turn-off Mode; V <sub>DIAG</sub> = 1V                       | -   | 3     | 10    | μS    |

| t <sub>DAIGFB(min)</sub> | Minimum Diagnostic Flyback Time                                                 |                                                                  | 26  | 42    | 50    | μS    |

| t <sub>DIAG(prot)</sub>  | Protection Diagnostic Pulse Width                                               | Over-voltage, Under-voltage,<br>Over-current, Over-temperature   | 2   | 7     | 10    | μS    |

| V <sub>DIAG(low)</sub>   | Diagnostic Voltage Low                                                          | I <sub>DIAG</sub> <= 1mA,<br>Diagnostic output active            | -   | -     | 0.9   | V     |

|                          |                                                                                 | <b>°</b>                                                         |     |       |       |       |

Integrated protection functions, as described in this data sheet, are designed to prevent the destruction of the IC and these fault conditions are considered 'outside' the normal operating ranges. It is important to note that the protection functions integrated into this device are NOT designed for continuous repetitive operation.

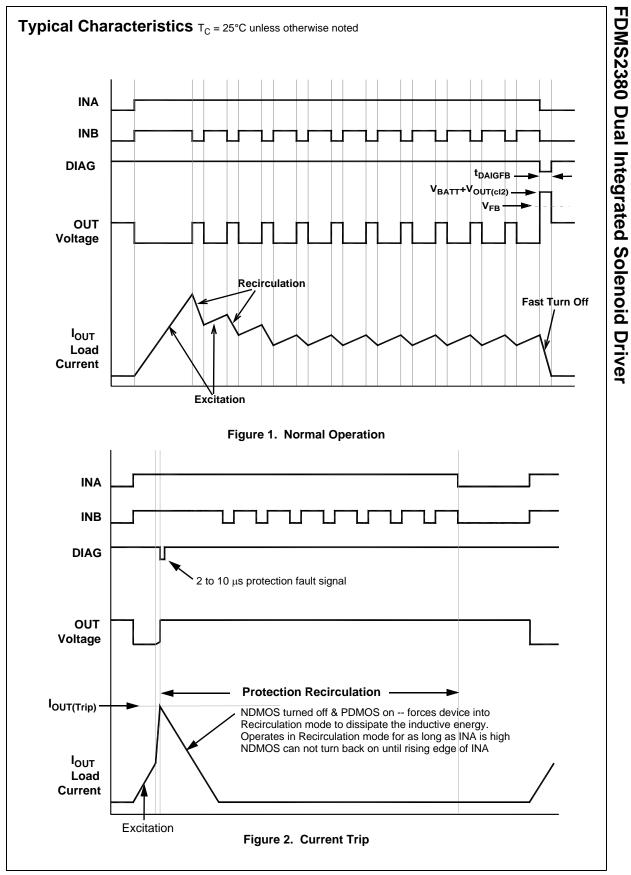

#### Normal operation (see figure 1)

**STANDBY MODE, INA = INB = 0** In the Standby mode, INA and INB are in the logic low state and there is no output current flow through solenoid coil. Both the PDMOS and NDMOS output power transistors are in their off state. This is the condition either at the start of a cycle to activate the solenoid or after a flyback signal has been generated.

**EXCITATION MODE, INA = INB = 1** In the Excitation mode, INA and INB are in the logic high state and the NDMOS power transistor is turned on to sink current through the coil connected to the positive supply.

The output current rises in this condition until limited by either the coil resistance or the FDMS2380 if the current reaches the output current trip level  $I_{OUT(trip)}$  in which case the FDMS2380 will turn off the NDMOS and issue a protection diagnostic signal.

**RECIRCULATION MODE, INA = 1, INB = 0** The Recirculation mode normally follows the Excitation mode. In this mode the NDMOS is turned off and the PDMOS is on. The current in the coil, connected to the output, is recirculated to the positive power supply pin through the low impedance path of the recirculation diode and the PDMOS transistor. In the Recirculation mode the coil current  $I_{OUT}$  slowly decays due to the impedance of the inductive load and the forward voltage drop across the FDMS2380 recirculation path.

The FDMS2380 will also enter the Recirculation mode during over-voltage, over-current, and over-temperature conditions as a means to limit the power dissipation in the device.

FAST TURN-OFF MODE, INA -> 0 The fast turn-off mode is initiated whenever the INA pin transitions from a logic high to low state with INB also in a logic low state. In this mode the output voltage "flies back" to  $V_{BATT}+V_{OUT(cl2)}$  where it is clamped by the FDMS2380 and the coil current is recirculated through the device back to the V<sub>BATT</sub> supply. The larger amplitude flyback voltage causes the coil current to rapidly discharge shutting off the solenoid. This flyback condition shall last as long as the output voltage is greater then  $V_{\text{BATT}}$  and less then  $V_{\text{OUT(cl1)}}.$  During this time, the output diagnostic pin DIAG is driven low for the duration of the flyback pulse. Any output flyback pulses which are less then the period  $t_{\mathsf{DIAGFB}(\mathsf{min})}$  will have its corresponding diagnostic pulse lengthened to a minimum of t<sub>DIAGFB(min)</sub> to help identify the flyback condition from a possible protection diagnostic fault.

If an under-voltage condition exists the flyback diagnostic pulse will be blocked, however, a flyback diagnostic pulse is generated if the flyback condition is still present at the end of the under-voltage condition.

For inputs INA and INB in the logic low state the NDMOS and PDMOS transistors will be off. Exceptions to this condition are; during an alternator load dump event that could drive the output to greater then  $V_{OUT(cl1)}$  the NDMOS will clamp the output voltage, and during a flyback event the PDMOS will clamp the output to  $V_{OUT(cl2)}$ .

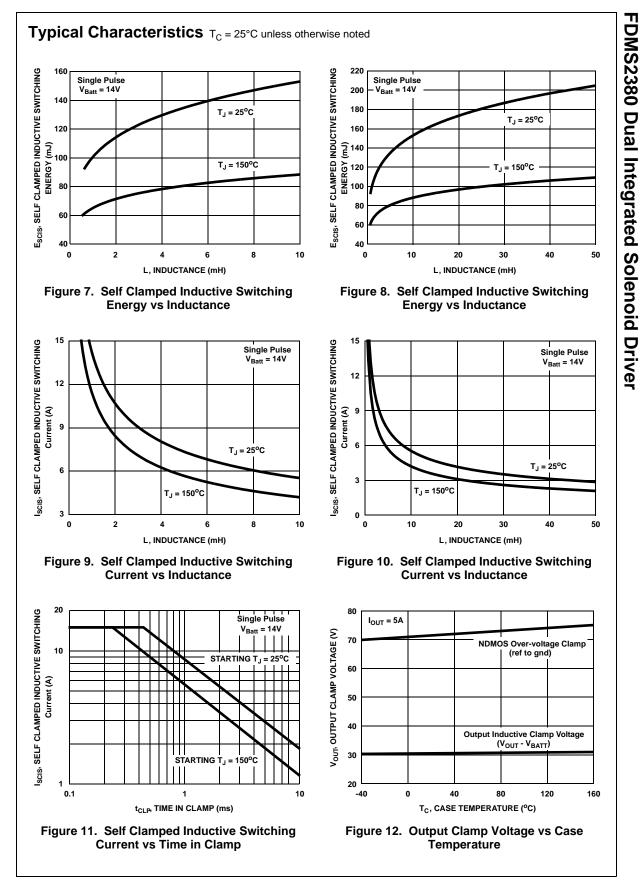

Using the curves from figures 7 through 12, the driving parameters (e.g., maximum duty cycle, etc.) and/or the

solenoid characteristics (e.g., coil resistance or coil inductance) must be checked to ensure the FDMS2380 is not damaged by SCIS (self-clamped inductive switching) related overstress.

SOFT SHORT TEST MODE, INA = 0 INB = 1 This test mode is used for detecting an output ground fault. The Soft Short mode is initiated any time INA=0 and INB=1 when in the Standby mode. The input conditions need to be held for a minimum of 2 ms to allow for the timing of the Soft Short detection circuit. After this setup time the FDMS2380 switches in a resistance (R<sub>SS</sub>) of approximately 75 ohms between V<sub>BATT</sub> and the output (OUT) pin. This resistance, connected in parallel to the load, acts as an additional pullup impedance to the positive power supply. To minimize power dissipation in the event of an output ground fault, the output pull-up resistor, activated in the Soft Short mode, is only switched on for a period of Tss by the FDMS2380. Regardless if the INA and INB signals remain in the Soft Short state for a longer period of time. Immediately prior to the end of this period, the output voltage  $V_{\mbox{OUT}}$  is compared to the  $V_{BATT}$  supply voltage and if the difference is greater then  $V_{OUT(ss)}$  the diagnostic pin DIAG is pulled low. The diagnostic pin will stay activated until the Soft Short mode is terminated by a change of the INA or INB inputs.

To minimize the power dissipation the Soft Short test mode should not be restarted sooner than 10 ms after a previous Soft Short test.

#### **Self-Protection Functions**

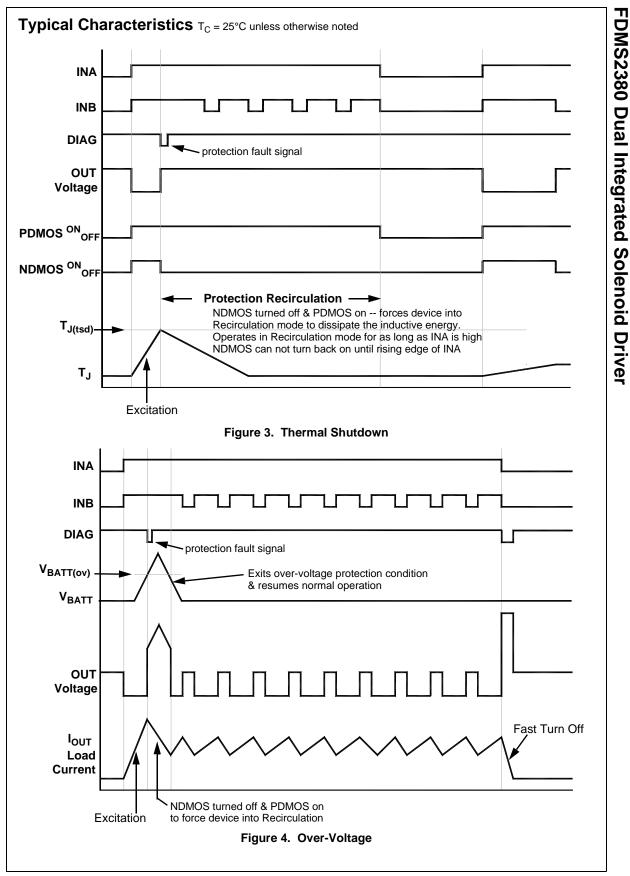

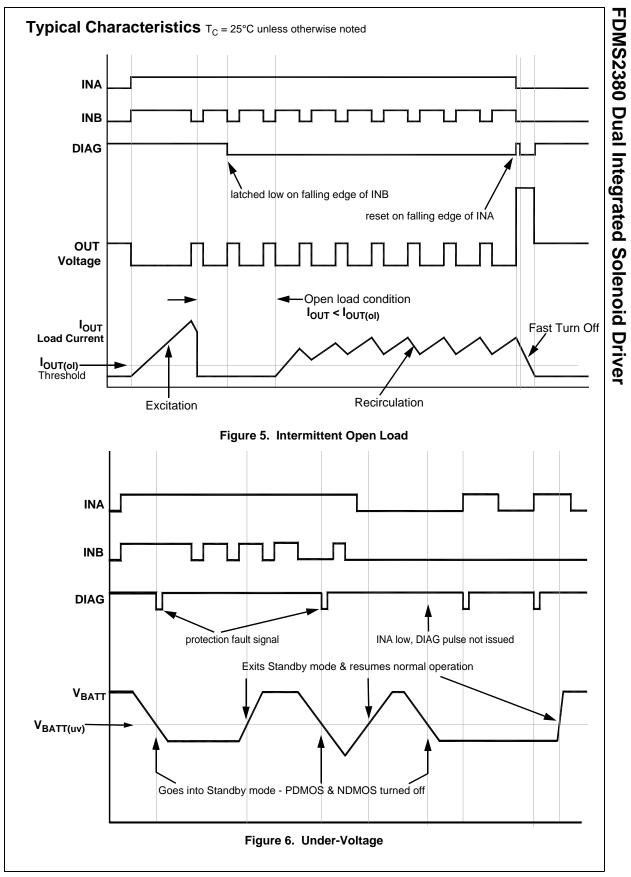

Refer to figures 2 through 6 for self-protection waveforms. All self-protection modes except over-voltage and undervoltage are reset when INA goes to logic 0. When a selfprotection condition is detected the FDMS2380 will issue a protection fault on the diagnostic pin. This fault condition is signaled by a 2  $\mu$ s to 10  $\mu$ s pulse t<sub>DIAG(prot)</sub> on the diagnostic pin DIAG. If the INA pin is activated while the condition setting the protection fault is still active additional protection fault diagnostic pulses will be issued.

**Current Trip** (see figure 2) Anytime during Excitation mode, if the current in the NDMOS rises above the  $I_{OUT(trip)}$  level, the FDMS2380 will turn off the NDMOS and enter into the Recirculation mode and issue a 2  $\mu$ s to 10  $\mu$ s protection fault pulse on the diagnostic pin DIAG. The device will remain in this Recirculation mode as long as the INA pin remains high and is terminated with the falling edge of INA.

**Thermal Shutdown** (see figure 3) The FDMS2380 is internally protected against over-temperature conditions by a temperature sensing circuit. When the FDMS2380 junction temperature exceeds the protection limit, T<sub>J(tsd)</sub>, thermal shutdown of the device will occur. Upon entering thermal shutdown a 2  $\mu$ s to 10  $\mu$ s protection fault signal is activated in the DIAG pin. In thermal shutdown, the NDMOS is switched off and the FDMS2380 operates in recirculation to discharge the energy in the load coil and minimize power dissipation. The FDMS2380 will remain in this state until INA is to logic 0. A protection fault signal will be issued each time INA is brought to a logic high while the overtemperature conditions exists.

**Overvoltage** (see figure 4) While in the Excitation mode if the V<sub>BATT</sub> pin rises above the over-voltage threshold, V<sub>BATT(ov)</sub>, the FDMS2380 is forced into the Recirculation mode and a protection fault signal on the diagnostic pin DIAG is generated. This condition is not reset by INA going low but by the voltage of the V<sub>BATT</sub> pin returning below the V<sub>BATT(ov)</sub> level. A protection fault pulse will be issued each time the device is driven into the Excitation state while the over-voltage condition exists.

The FDMS2380 is designed with a fast responding overvoltage circuit that disables the output slope control circuit which minimizes radiated EMI. However, voltage transitions on the V<sub>BATT</sub> pin which exceed 30 volts above the battery need to be limited to a rise time no faster then 2.2 V/µs through the use of a power supply bypass capacitor.

**Undervoltage** (see figure 6) The FDMS2380 will operate down to a minimum voltage of V<sub>BATT(uv)</sub>. If the battery supply drops below this minimum voltage the device is forced into the Standby mode. If INA is high during this condition a 2  $\mu$ s to 10  $\mu$ s protection fault pulse is issued on the diagnostic DIAG pin. In addition, a diagnostic pulse will be generated each time INA transitions from a low to a high logic level while remaining in this under-voltage condition.

The FDMS2380 will return to normal operation when  $\mathrm{V}_{\mathrm{BATT}}$  is 6 volts or greater.

#### **Diagnostic Functions**

**Open Load Detect** (see figure 5) While INA and INB are high, if the load current fails to rise above the open load current level,  $I_{OUT(ol)}$ , before INB transitions low an open load diagnostic fault will be issued. The diagnostic pin will be driven low on the falling edge of the INB signal and remain low until INA is returned to a logic 0 condition. The open load detect mechanism senses current flowing through the NDMOS at the falling edge of the INB signal. If an open load condition exists during the Excitation phase but is corrected before the INB falling edge the open load diagnostic fault would not be generated.

The open load detection circuit does not alter the operation of the FDMS2380 and the PDMOS and NDMOS output transistors will be driven into the operational modes as commanded by the INA and INB inputs.

If during the detection of the open load condition a protection fault condition also arises, the open load diagnostics will be terminated and then after a 2  $\mu s$  to 10  $\mu s$  blanking period the protection diagnostic will be generated.

| Conditions                                                                      | INA | INB | NDMOS                  | PDMOS                               |  |

|---------------------------------------------------------------------------------|-----|-----|------------------------|-------------------------------------|--|

| Standby Mode:                                                                   | L   | L   | OFF                    | OFF                                 |  |

| Soft Short Test Mode                                                            | L   | Н   | OFF                    | ON                                  |  |

| Excitation Mode: (No protection faults)                                         | Н   | Н   | ON                     | ON                                  |  |

| Recirculation Mode                                                              | Н   | L   | OFF                    | ON                                  |  |

| Fast Turn-off Mode: V <sub>FB</sub> < V <sub>OUT</sub> < V <sub>OUT(cl1</sub> ) | L   | L   | OFF                    | $V_{OUT}$ clamped to $V_{OUT(cl2)}$ |  |

| Alternator Load Dump: V <sub>OUT</sub> > V <sub>OUT(cl1)</sub>                  | L   | х   | NDMOS in UIS operation | NA                                  |  |

| Thermal Shutdown: $T_J > T_{J(tsd)}$                                            | Н   | Х   | OFF                    | ON                                  |  |

| Current Trip: I <sub>OUT</sub> > I <sub>OUT(trip)</sub>                         | Н   | Н   | OFF                    | ON                                  |  |

| Overvoltage: V <sub>BATT</sub> > V <sub>BATT(ov)</sub>                          | Н   | Н   | OFF                    | ON                                  |  |

| Undervoltage: V <sub>BATT</sub> < V <sub>BATT(uv)</sub>                         | Н   | Х   | OFF                    | OFF                                 |  |

| Open Load: $I_{OUT} < I_{OUT(ol)}$ refer to Open Load waveforms (Figure 5)      | -   | -   | -                      | -                                   |  |

#### **Operational Truth Table**

H = High, L = Low, X = Don't Care

General operation INA and INB are standard logic inputs that control Standby, Excitation, Recirculation, Diagnostics, and Fast turn-off modes in the FDMS2380.

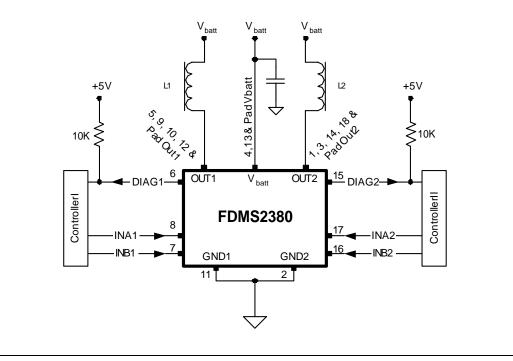

# **Typical Application Circuit**

The following schematic of an FDMS2380 used in a basic application is just one of several possible variations for this device. It shows two external and independent controllers, one for each channel, and two solenoids being controlled by the FDMS2380. Furthermore, it shows the external local V<sub>BATT</sub> bypass capacitor, the details of which are discussed in the Maximum Ratings section. The FDMS2380 ground pins GND1 and GND2 are fully isolated; therefore, they are normally connected together on the PCB.

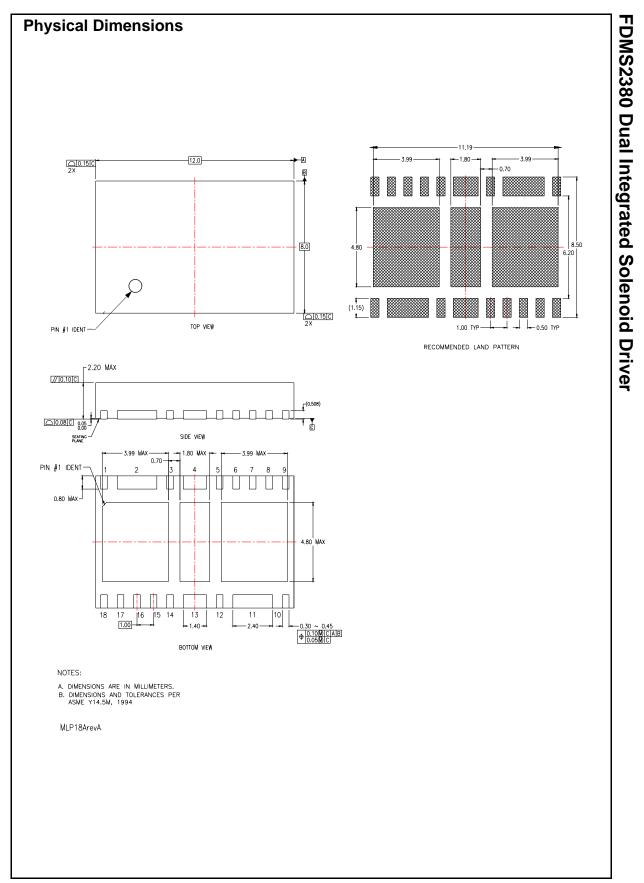

When designing the PCB for the FDMS2380 the user needs to provide as low a thermal impedance as is possible for both the V<sub>BATT</sub> and OUT[1,2] paddles on the bottom of the package. The power density in the dual integrated solenoid driver can be quite large and care should be taken to optimize the thermal impedance of the system to maximize the power handling capability of the device while minimizing the maximum operating temperature.

SEMICONDUCTOR

#### TRADEMARKS

The following are registered and unregistered trademarks and service marks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.

ACEx® Green FPS™ Build it Now™ CorePLUS™ CROSSVOLT™ CTL™ Current Transfer Logic™ EcoSPARK<sup>®</sup> Fairchild® Fairchild Semiconductor® FACT Quiet Series™ FACT FAST® FastvCore™ FPS™ FRFET® Global Power Resource<sup>™</sup>

Green FPS™ e-Series™ GTO™ i-Lo™ IntelliMAX™ ISOPLANAR™ MegaBuck™ MICROCOUPLER™ MicroFET™ MicroPak™ MillerDrive™ Motion-SPM™ **OPTOLOGIC<sup>®</sup> OPTOPLANAR<sup>®</sup>** PDP-SPM™ Power220®

Power247® **POWEREDGE<sup>®</sup>** Power-SPM™ PowerTrench<sup>®</sup> Programmable Active Droop™ QFET<sup>®</sup> QS™ QT Optoelectronics™ Quiet Series™ RapidConfigure™ SMART START™ SPM® STEALTH™ SuperFET™ SuperSOT™-3 SuperSOT™-6

SuperSOT<sup>™</sup>-8 SyncFET™ The Power Franchise<sup>®</sup>

# p<sup>th</sup>ower

franchise TinyBoost™ TinyBuck™ TinyLogic® **TINYOPTO™** TinyPower™ TinyPWM™ TinyWire™ µSerDes™ UHC® UniFET™ **VCX™**

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

# PRODUCT STATUS DEFINITIONS

#### **Definition of Terms**

| Datasheet Identification | Product Status         | Definition                                                                                                                                                                                                     |

|--------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative or In Design | This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                             |

| Preliminary              | First Production       | This datasheet contains preliminary data; supplementary data will be<br>published at a later date. Fairchild Semiconductor reserves the right to<br>make changes at any time without notice to improve design. |

| No Identification Needed | Full Production        | This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design.                                                         |

| Obsolete                 | Not In Production      | This datasheet contains specifications on a product that has been discontinued by Fairchild Semiconductor. The datasheet is printed for reference information only.                                            |

Rev. 131